| 您现在的位置:首页 > 技术资料 |

|

基于DAC5687的宽带数字中频系统设计 DAC5687是美国TI公司推出的一款高速、高性能、双通道16位的D/A转换芯片,其最高采样速率可达500MSPS。DAC5687专用于3G基站信道传输、3G直放站、数字卫星等对功耗、价格、体积要求比较严格的通信系统中。其内部基本结构如图1所示,主要有6个信号处理模块:固定插值滤波器FIR1、FIR2、FIR3和带有32位数控振荡器的精混频器、正交调制校正模块和粗混频器。DAC5687可以通过微控制器进行灵活的配置,是一款基于软件无线电的半定制ASIC芯片。 根据软件无线电中频数字化的基本思想,本文提出一种基于DAC5687的宽带数字中频系统的设计方案。 1 宽带数字中频系统的总体设计 1.1 系统简介 数字中频系统的主要特点就是利用DSP器件功能强大、灵活的优势,处理数字化的模拟信号,减少模拟环节;同时,为了减轻DSP的处理压力,数字中频还起到采样速率变换的作用。系统先利用A/D带通采样将输入信号变成低中频信号,经FPGA滤波处理后,再通过DAC5687实现上变频和D/A转换,整体系统硬件电路如图2所示。本文采用WCDMA测试模式1(TEST mod-el1)作为输入测试信号,码片速率为3.84Mchip/s,单信道带宽为5MHZ。信号范围为132.5MHZ~147.5MHZ,采用3个相邻信道进行处理,则每个信道的中心载波频率分别为:135MHZ、140MHz、145MHZ。

系统输入的抗混叠滤波器采用CETC公司推出的声表滤波器LBl40DS13。其中心频率为140MHz,3dB抑制带宽为16.9MHz,40dB抑制带宽为21.2MHz,插损典型值为9dB,滤波器传输时延为1.02微秒。 A/D转换器采用AD公司的AD6644,它的最高采样率可达65MSPS,分辨率为14位。在本系统中,它直接对中心频率140MHz、"整体带宽"15MHZ的中频信号进行带通采样,采样时钟取61MHz,采样后的信号中频为18MHZ,信号速率为61MSPS。 FPGA采用ALTERA公司的EP2C35F484C8,它内部含有33 216个逻辑单元,用户最大可定义的I/O管脚为322个。在本系统中,FPGA主要对A/D采样后的14位低中频信号进行滤波处理,然后输出16位数字信号给D/A转换器。 单片机采用ATMEL公司推出的AT89C51ED2系列,在本系统中用来配置DAC5687和FPGA。 D/A转换器采用美国TI公司推出的带有上变频功能的DAC5687,其主要作用是对信号进行上变频和D/A转换。 2 DAC5687的具体应用 2.1 工作模式 根据DAC5687内部结构的特点,结合精混频(FMIX)和粗混频(CMIX)模块,采用DAC5687的X4L FMIX CMIX模式。系统发射部分的基本框图如图3所示,单信道输入,其中Fin为测试信号的速率,Fsm为测试信号的中心频率(m=0,1,2,3,4,5)。FPGA输出的16位信号经过DAC5687内部混频后产生一个165MHZ的干扰信号,故外接一个LRC带通滤波器加以消除。18MHZ的输入中频测试信号经过发射部分后,输出79MHz的中频模拟 信号。 2.2 X41 模式下的信号处理过程 下面结合图3分析DAC5687中X4L模式下的信号处理过程。

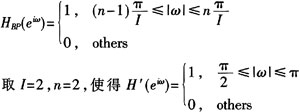

FIR3和FIR1幅频响应完全相同,如图4所示。FIR3的通带范围为: 在内插后需对信号进行低通和混频的处理。当混频的频率为Fin(内插前的信号速率)时,设输人中频为,则内插低通滤波后再进行混频,如果取"差频",则输出中频为Fin-?,输出信号速率为2Fin。这种方法可等效看作是一种"高通"的形式,相当于在内插后设置一带通滤波器HBP(eiω):

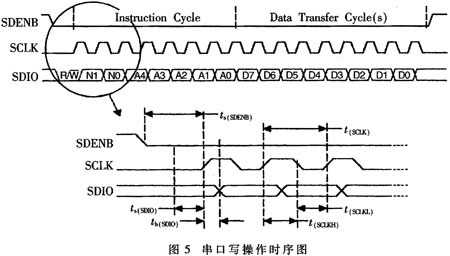

实际上为一高通滤波器。所以可以把这种"低通+混频"的处理方式看作是一种内插后"高通"滤波的形式。相当于借助"高通"滤波器选择内插后的高频分量Fin-?,滤掉了含有?的低频信号分量。X4L FMIX CMIX模式实际上起到了上变频作用,但不改变信号本身的频谱结构。 DAC5687提供了一个灵活的同步串行接口,可以对其32位的寄存器进行读写访问。其主要接口引脚如表1所示。

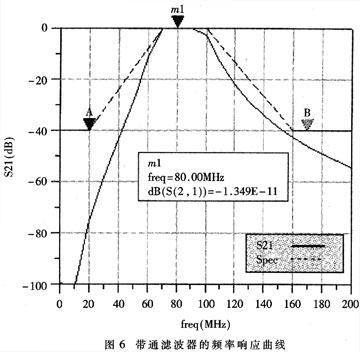

由于DAC5687的输出信号伴有FOUT'=165MHZ的干扰频率,在这里用ADS2003A设计了一个4阶的LRC带通滤波器,频率响应如图6所示。其性能基本满足要求。

(2) 系统中利用等效"高通"滤波器时,会产生频谱镜像。采用X4、X8模式,并经过2次"高通"可以避免此问题。但经过第一次"高通"后,应考虑到后一级FIR滤波器的通带范围,避免混频后信号被下一级滤波器完全抑制,难以达到设计要求。 (3) 由于D/A转换速率较高,DAC5687的时钟源设计就显得非常关键。可采用TI公司的CDCM7005结合VCXO或者VCO器件来保证良好的时钟质量,整个系统带有模数混合电路。在制作PCB板时,应考虑到信号完整性问题。 在基于图2的实验硬件平台上,DAC5687对FPGA送出的WCDMA信号进行处理。将中频18MHZ、速率61MHz的低速低中频信号上变频到中频为79MHz、速率达到244MHz的高速信号。经实际电路验证,其结果与设计要求完全吻合。 基于DAC5687的数字中频系统最大的优势是利用了软件无线电的基本思想,能根据具体的系统方案灵活而合理地选择DAC5687的工作模式,实现设计要求;无需在FPGA中实现混频、上变频等极易受接口速率制约的功能,不用在FPGA后外接DUC器件;降低了FPGA部分设计的难度,简化了系统的整体设计,而且可以选择合适容量的FPGA芯片,使得FPGA的利用率达到最大化,从而合理有效地降低了系统成本。

| ||||||||||||||